Fredrik Pettersson

# Paper- and Membrane-Based Ion-Modulated Electronics

## Fredrik Sebastian Pettersson

Born 1981 in Porvoo, Finland Obtained his M.Sc. degree at Åbo Akademi University in 2008. Joined the Organic Electronics group at the physics department in 2007.

## Paper- and Membrane-Based Ion-Modulated Electronics

## **Fredrik Pettersson**

Physics Center for Functional Materials Faculty of Science and Engineering Åbo Akademi University Turku, Finland, 2015

#### **Supervisor**

Professor Ronald Österbacka Åbo Akademi University, Finland

#### **Pre-examiners**

Professor Andrew Steckl

University of Cincinnati, United States

Professor Krizstian Kordas

University of Oulu, Finland

#### Opponent for the public defense

Doctor Mihai Irimia-Vladu Joanneum Research Forschungsgesellschaft, mbH, Austria

ISBN 978-952-12-3262-6 Painosalama Oy, Turku, Finland 2015

## **Acknowledgements**

The research presented in my thesis is mainly based on the work done at the physics department at the Faculty of Science and Engineering at Åbo Akademi University. I wrote the thesis as a member of the Organic Electronics group, which is part of the Center for Functional Materials (FUNMAT) and a National Center of Excellence. The work has been partially funded by the Academy of Finland and the Finnish Funding Agency for Innovation, through different projects, and several travel grants have been awarded by Svenska Tekniska Vetenskapsakademin i Finland, the Magnus Ehrnrooth Foundation and the Swedish Cultural Foundation in Finland.

I would especially like to thank my supervisor Prof. Ronald Österbacka, who not only allowed me the opportunity to complete my Master's thesis and my Doctoral thesis in the Organic Electronics group, but also provided me with funding and the all-important guidance to reach the last sentence of this thesis. He has also provided me with the tools I needed to be able to work independently and also managed to create an inspiring research environment within the research group, where fruitful discussions and collaborations are plentiful. I would also like to thank our laboratory engineer, Dr. Kjell-Mikael Källman, who has helped me build many wonderful contraptions and solve many engineering related dilemmas. Majsa Tamminen has helped me through most of the bureaucracy that I have faced over the years as a student at Åbo Akademi University.

I would like to acknowledge all the people that I have had the pleasure of working with over the years. I would, especially, like to thank Niklas Björklund and Dr. Nikolai Kaihovirta for teaching me about transistors, Dr. Tommi Remonen for his insights in chemistry and innovative thinking, Yanxi Zhang for his work on the blends and David Adekanye for his contribution in building the logic gates. Also, a special thanks to Carl-Johan Wikman, Janne Koskela, Dr. Roger Bollström and Dr. Anni Määttänen for the collaboration.

I would like to thank the Teachers, Professors and Senior Scientists whom without none of the work presented in my thesis would have been possible. Apart from Prof. Österbacka I wish to thank Prof. Markus

Lindberg, Prof. Carl-Eric Wilén, Dr. Ari Kilpelä, Dr. Jari Kilpelä, Prof. Martti Toivakka, Prof. Jouko Peltonen, Doc. Johan Linden and Dr. Tom Lönnroth.

I am grateful for having being able to study and work in such a friendly and inviting work environment as the physics department, from the personnel to the students, and I wish to, especially, acknowledge my good friends and classmates Joakim Slotte, Daniel Lindberg and Kjell Helenius.

I would like to give my thanks to my parents who have always supported me and encouraged me and thereby made my academic journey possible. I would like to thank my whole family and my friends for making this journey an enjoyable one.

Finally, I would like to thank my Sarah for helping me conclude this thesis, for encouraging me to always fulfill myself and for her endless love.

Turku 5.8 2015

Fredrik Pettersson

## **Contents**

| Acknowledgements                               | i   |

|------------------------------------------------|-----|

| Contents                                       | iii |

| List of included publications                  | v   |

| Author's contribution                          | vi  |

| List of other publications and patents         | vii |

| 1. Introduction                                | 1   |

| 1.1. Background                                | 1   |

| 1.1.1. Transistors and logic gates             |     |

| 1.1.2. Energy storage units                    | 2   |

| 1.2. Transistors                               | 3   |

| 1.2.1. Organic Field-Effect Transistors        | 3   |

| 1.2.2. Ion-Modulated Transistors               | 7   |

| 1.3. Logic Circuits                            | 13  |

| 1.3.1. Inverters                               | 14  |

| 1.3.2. Ring-Oscillators                        | 15  |

| 1.3.3. NOR-Gates                               | 16  |

| 1.3.4. SR-Latches                              | 17  |

| 1.4. Supercapacitors                           | 19  |

| 2. Experimental                                | 23  |

| 2.1. Materials and Methods                     | 23  |

| 2.1.1. Substrates                              | 23  |

| 2.1.2. Electrodes                              | 25  |

| 2.1.3. Semiconductors                          | 28  |

| 2.1.4. Ion-Conductors                          | 32  |

| 2.2. Measurements                              | 35  |

| 2.2.1. Electrical Characterization             | 35  |

| 2.2.2. X-Ray Photoelectron Spectroscopy        | 38  |

| 2.2.3. Contact Angle- and Optical Measurements |     |

| 2.2.4 Atomic Force Microscopy                  | 39  |

| 3. Results and Discussion                                                                                        | 41  |

|------------------------------------------------------------------------------------------------------------------|-----|

| 3.1. Patterned Membrane as Substrate and Electrolyte in Depletion- an Enhancement Mode Ion-Modulated Transistors |     |

| 3.2. Ion-Modulated Transistors on Paper using Phase-separated Semiconductor/Insulator Blends                     | 43  |

| 3.3. Environmentally Friendly Transistors and Circuits on Paper                                                  | 47  |

| 3.4. Printed Environmentally Friendly Supercapacitors with Ionic Liquid Electrolytes on Paper                    |     |

| 4. Summary                                                                                                       | 57  |

| 5. Conclusion and Outlook                                                                                        | 59  |

| Svensk resumé                                                                                                    | 61  |

| References                                                                                                       | 63  |

| Paper I                                                                                                          | 73  |

| Paper II                                                                                                         | 85  |

| Paper III                                                                                                        | 95  |

| Paper IV                                                                                                         | 107 |

## List of included publications

Paper I. Patterned Membrane as Substrate and Electrolyte in Depletion- and Enhancement Mode Organic Transistors,

F. Pettersson, J. Koskela, C.-J. Wikman, T. Remonen, C.-E. Wilén,

A. Kilpelä and R. Österbacka,

IEEE Journal of the Electron Devices Society, 3, 58 (2015)

Paper II. Ion-Modulated Transistors on Paper using Phase-separated Semiconductor/Insulator Blends,

F. Pettersson, R. Österbacka, J. Koskela, A. Kilpelä, T. Remonen, Y. Zhang, S. Inkinen, C.-E. Wilén, R. Bollström, M. Toivakka, A. Määttänen, P. Ihalainen and J. Peltonen,

MRS Communications, 4, 51 (2014)

Paper III. Environmentally Friendly Transistors and Circuits on Paper,

F. Pettersson, T. Remonen, D. Adekanye, Y. Zhang, C.-E. Wilén

and R. Österbacka,

ChemPhysChem, 16, 1286-1294 (2015)

Paper IV. Printed Environmentally Friendly Supercapacitors with Ionic Liquid Electrolytes on Paper,

F. Pettersson, J. Keskinen, T. Remonen, L. von Hertzen, E. Jansson, K. Tappura, Y. Zhang, C.-E. Wilén and R. Österbacka, Journal of Power Sources, 271, 298 (2014)

#### Author's contribution

The work presented in this thesis is mainly based on experiments planned, performed and analyzed by the author. Some particular contributions to the different papers by the author are listed below:

- Paper I. The author of this thesis did all the experimental work presented in this paper. Electrical expertise was provided by Janne Koskela and the membranes were provided by Carl-Johan Wikman. The manuscript was written by the author and was finalized together with the co-authors.

- Paper II. The author of this thesis did all the experiments presented in the paper. The original idea of using phase-separation in our transistors is attributed to Daniel Tobjörk and further developed by the author in collaboration with Tommi Remonen and Yanxi Zhang. The manuscript was written by the author and finalized together with the co-authors.

- Paper III. The author of this thesis did all the experiments presented in this paper except the logic gates presented at the end of the paper. They were done by David Adekanye under the supervision of the author. The deep eutectic mixture concept of electrolytes was developed by Tommi Remonen. The manuscript was written by the author and finalized together with the co-authors.

- Paper IV. The author of this thesis did all the experimental work presented in this paper except fabrication of the AC electrodes and the confocal imaging. The electrodes were done by Jari Keskinen and Leo von Hertzen and the confocal imaging by Max Johansson. The manuscript was written by the author, Jari Keskinen and Tommi Remonen and finalized together with the co-authors.

## List of other publications

- Paper 1. An Impedimetric Study of DNA Hybridization on Paper-Supported Inkjet-Printed Gold Electrodes,

P. Ihalainen, F. Pettersson, M. Pesonen, T. Viitala, A. Määttänen,

R. Österbacka and J. Peltonen, Nanotechnology, **25**, 094009 (2014)

- Paper 2. *Impact of humidity on functionality of on-paper printed electronics*, R. Bollström, F. Pettersson, P. Dolietis, J. Preston, R. Österbacka and M. Toivakka, Nanotechnology, **25**, 094003 (2014)

- Paper 3. Cellulose-based ionogels for paper electronics, S. Thiemann, S. Sachnov, F. Pettersson, R. Bollström, R. Österbacka, P. Wasserscheid and J. Zaumseil, Advanced Functional Materials, **24**, 625 (2014)

- Paper 4. Origin of equilibrium charges in poly(3-hexylthiophene):[6,6] phenyl-C61-butyric acid methyl ester solar cell devices,

M. Nyman, F. Pettersson and R. Österbacka, Chemical Physics,

404, 60 (2012)

- Paper 5. Controlling the turn-on-voltage in low-voltage Al<sub>2</sub>O<sub>3</sub> organic transistors with mixed self-assembled monolayers,

N. Björklund, F. Pettersson, D. Tobjörk and R. Österbacka,

Synthetic Metals, **161**, 743 (2011)

- Paper 6. Enhanced performance of printed organic diodes using a thin interfacial barrier layer,

K. Lilja, H. Majumdar, F. Pettersson, R. Österbacka and T. Joutsenoja, ACS Applied Materials & Interfaces, 3, 7 (2011)

- Paper 7. All-printed low-voltage organic transistors,

D. Tobjörk, N. Kaihovirta, T. Mäkelä, F. Pettersson and R. Österbacka, Organic Electronics, **9**, 931 (2008)

## List of patents

Patent 1. Electroactive Blends and Layers, and Devices made from these, WO 2015028700 A1, T. Remonen, F. Pettersson. R. Österbacka, Y. Zhang, D. Tobjörk, S. Inkinen and C.-E. Wilén

#### 1. Introduction

This chapter introduces the general fields of the transistor and its application in logic circuits followed by energy storage devises. In Section 1.2, the organic field-effect transistor as well as the different models of organic ion-modulated transistors (IMTs) used and the special methods developed to create paper transistors are described. In Section 1.3, the logic gates developed using paper- and membrane-based transistors are presented and finally in Section 1.4 the environmentally friendly supercapacitor (SuC) on paper is presented.

### 1.1. Background

#### 1.1.1. Transistors and logic gates

A transistor [1,2] is a three terminal device that is used in electronic circuits to control a large signal between two of the transistor terminals by applying a small signal between two other terminals. As a small change in the input signal translates to a large change in the output signal, the transistor can be used as an amplifier. This is also known as gain. The most common transistor type used in modern digital and analog circuitry is the metal oxide semiconductor field-effect transistor (MOSFET). [3] It was invented in 1959 at Bell Labs and was used in the first microprocessors created. [4] In the early 1970s, p-type and n-type MOSFETs (PMOS and NMOS, respectively) were used separately in microprocessors. Later on they were combined to create complementary-MOS (CMOS) technology. [5] The advantage with CMOS is that it has low power consumption and is not prone to overheating, e.g. when compared to NMOS- or PMOS-only electronics. [6] This sparked the interest in these types of field-effect transistors and much effort was put into researching and developing them further and with the development of clean rooms etc. smaller and more efficient transistors were made. This eventually led to the world's first mass-produced, truly portable, personal computer at the beginning of the 1980s. This intensive research also led to other types of transistors being developed, for this thesis the most important being the organic field-effect transistor (OFET), demonstrated by Tsumura et. al. [7] in 1986, as one of the first of its kind and immediately after that, in Finland, a similar OFET was demonstrated by Kuivalainen et. al. [8] The main reasons for developing the OFET has been environmental, economic as well as the fact that organic semiconductors can be solution-processable and large-area fabrication processes can be utilized without expensive clean rooms. [9,10] Another advantage is that organic semiconductors can be flexible and, thus, roll-to-roll (R2R)-compatible fabrication

processes can be used to create cheap transistors on many substrates not suitable e.g. for silicon-based electronics. [11–13] Flexible substrates such as PET, paper and even textile fibers have been used to fabricate transistors on. [14] This opens up possibilities to create all imaginable sorts of applications, such as sensors and displays printed directly on food packages and shipping boxes, battery charging and health monitoring devices incorporated into the textile of clothing, bendable displays for wrist watches, solar cells painted directly onto roofs, light emitting paint on walls etc. Organic based electronics is also used when interfacing with live tissue [15,16] and has even been shown to outperform inorganic electronics in that area. [17]

In this thesis, methods to create transistors on rough and absorptive substrates are being investigated, as well as making the devices more environmentally friendly and also, improving the switching speeds of the devices. Each of the methods presented to solve these issues are usually accompanied by some other form of decrease in performance. The trick is to evaluate the trade-offs and try to find an optimized solution that makes the device as good as possible within the set parameters.

#### 1.1.2. Energy storage units

The Volta cell was invented in the 1800s and consisted of zinc and copper electrodes separated by cardboard and used brine as the electrolyte. [18] During operation, the cell utilizes electrochemically stored energy so that the zinc is being oxidized and releases ions into the electrolyte, leaving electrons in the metal that join with hydrogen ions in the electrolyte through an external connection to the copper electrode, creating hydrogen gas. As the zinc is being dissolved into the electrolyte, the cell is non-rechargeable. The present day cell was invented in 1949 and consisted of zinc and manganese electrodes and used alkaline electrolytes. The rechargeable battery was invented in 1859 (lead-acid) [19] and further improvements were made over the following years. The Li-ion battery, used in most electronic gadgets today, was invented in 1977. [20] The electric double layer capacitor (EDLC), invented in 1957 by H.I. Becker [21] and also the type of energy storage unit presented in this thesis, is both rechargeable and non-Faradaic. In the EDLC, which consists of two metal electrodes separated by a separator and electrolyte, the charges are stored electrostatically on the surface of the electrodes and no charge is being exchanged between the electrodes and electrolyte. The electrolytes and electrodes were further improved over the years but the same principal device is still used today in most EDLCs. Since the device structure is fairly simple, the electrodes can be made with carbon and the electrolyte can be almost any sort of ion-conducting material. The EDLC model is a superb

alternative for developing environmentally friendly energy storage devices, since the fabrication processes are roll-to-roll compatible and the materials used can be cheap and environmentally friendly. Supercapacitor is the term that will be used in this thesis when describing these types of devices. The term is a product name of the Nippon Electronic Company presented in 1971 [22] referring to the large area of the electrode materials used, in this case activated carbon-covered aluminum electrodes as well as the extremely high capacitances that are achievable when utilizing EDLs. The abbreviation SuC will be used for the term supercapacitor so not to confuse the reader with the abbreviation for the term semiconductor.

#### 1.2. Transistors

This section on transistors is divided into two parts; the first one describing the OFET and how to characterize it and in the second one, the ion-modulated transistor, the transistor model used in this thesis, is presented in more detail.

#### 1.2.1. Organic Field-Effect Transistors

The organic field-effect transistor (OFET) [7,23–28] structure is based on the thin film transistor (TFT) structure introduced by Weimer in 1962, [29] where all the layers of the device are thin and have been deposited, in some fashion, onto an insulating substrate. The main difference is that the OFET incorporates an organic semiconductor as opposed to an inorganic one that the presented TFTs used. The different parts of an OFET are the source- and drain electrodes, the semiconductor layer, the gate insulator layer and the gate electrode. These can be applied in different orders to create different transistor structures. It is important that the gate is separated from the semiconductor (and source- and drain electrodes) by the gate insulator and that the semiconductor is in contact with the source- and drain electrodes. An example transistor structure is drawn in Figure 1.1. The bottomgate, top-contact structure has the gate on the bottom, separated from the semiconductor by the insulator, and the source and drain electrodes on top. If the gate is un-biased and a potential is applied over the source and drain, no current will flow through the device as the semiconductor is non-conductive in this state. If a negative potential is applied to the gate (p-channel), the insulator will become polarized and charges will be injected into the semiconductor, from the source, in order to compensate for the resulting electric field. The injected, positive, charges will move to the semiconductor/insulator interface creating the transistor channel. Charges can now flow between the source and the drain and the transistor is said to be in the on-state. This electric field induced charge injection gives the organic field-effect transistor its name.

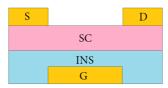

Figure 1.1. Top-contact bottom-gate configuration of an organic transistor. Source (S), drain (D) and gate (G) electrodes are colored in gold while the semiconductor (SC) and insulator (INS) are colored in pink and blue, respectively.

The OFET can be structured in many different ways and the materials can be applied in room temperature using a variety of techniques. [12] This makes it an appealing alternative to traditional silicon-based transistors. There are, however, some dimensional considerations that must be taken into account when fabricating OFETs. The channel length, e.g., should be minimized in order to maximize the current throughput. This can, however, be difficult to do using R2R-compatible fabrication techniques. The electrode overlap [30–32] is another issue that needs to be considered as stray capacitances cause decreased device performance, both in the form of speed and gate-leakage. The individual layers should also be as thin as possible, without causing short circuits, in order to increase the electric field strength and device switching speeds. [33–35]

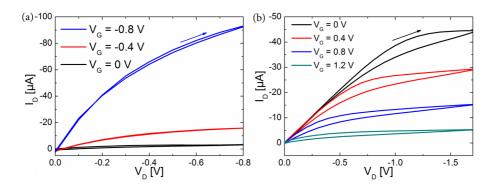

Even though the mechanism for charge transport in OFETs differ from that of traditional MOSFETs, the electrical response from the devices are similar and the traditional MOSFET equations can therefore be used to describe and characterize OFETs. The standard MOSFET Equations 1.1 - 1.5 below are taken from S. M. Sze's "Semiconductor Devices". [36] The same equations are also used to characterize IMTs, even though they differ even more in operation than OFETs do from MOSFETs. A typical way to characterize an OFET is to apply a constant voltage between the source- and drain electrodes, vary the gate voltage and measure the source-drain current,  $I_{DS}$ . This resulting *transfer* curve (see Figure 1.2 (a)) can then be used to determine a wide range of critical transistor values. An output curve, on the other hand, is measured by varying the source-drain voltage,  $V_{DS}$ , and measuring  $I_{DS}$ . Different constant gate voltages,  $V_G$ , are applied during these measurements and several traces of  $I_{DS}$ , at different  $V_G$ , are plotted as a function of  $V_{DS}$  (see Figure 1.2 (b)). The output curve can be used to determine when the transistor operates in the linear regime and when it operates in the saturated regime. When  $I_{DS}$  increases linearly with  $V_{DS}$ , the transistor is said to be operating in the linear regime. When  $I_{DS}$  stops increasing with increasing  $V_{DS}$  and saturates, the transistor is said to be operating in the saturated regime. The two regimes are marked in Figure 1.2 (b). In the linear regime ( $V_{DS} \ll V_G$ ) the current flow between the source and drain is not limited by the charge concentration in the channel and the current has an ohmic behavior.  $I_{DS}$  can be expressed as:

$$I_{DS}^{lin} = \frac{W}{L} \mu C_i \left( V_G - V_T - \frac{V_{DS}}{2} \right) V_{DS}$$

(1.1)

where W and L are the channel widths and lengths, respectively,  $\mu$  is the field-effect mobility of the charges in the channel,  $C_i$  is the insulator capacitance and  $V_T$  is the threshold voltage. In the saturated regime ( $V_{DS} > V_G$ ) the current flow becomes limited by the charge concentration in the channel and the current remains constant even if  $V_{DS}$  increases. This saturated current is then expressed by using Equation 1.1 and setting  $V_{DS} = V_G$ :

Figure 1.2. Typical (a) transfer- and (b) output curves of OFETs. Usually, the absolute drain/source-current ( $|I_{DS}|$ ) is shown on a logarithmic scale (black curve) while the square root of the same current ( $|I_{DS}|^{\frac{1}{2}}$ ) is shown on a linear scale (red curve) in the same graph. The gate current (not shown) is also typically drawn in the same graph on a logarithmic scale. The blue dashed line (B) is an extension of  $I_{DS}$  in the saturated regime. The threshold voltage  $(V_T)$  is determined by using the intersection of B and the  $V_G$ -axis. The green dashed line is used to determine the transconductance  $(g_m)$  and subthreshold swing (S). The output curve usually shows  $I_{DS}$  as a function of the drain/source-voltage  $(V_{DS})$  for different gate voltages  $(V_G)$ . The linear- and saturated regimes are separated by the blue dashed line.

The transfer curve is used to determine several critical transistor values and it can be measured both in the linear- and in the saturated regime. Note that only a transfer curve measured in the *saturated regime* is plotted in Figure 1.2. (a). The black curve is  $|I_{DS}|$  vs.  $V_G$  plotted on a log/lin scale while the red curve is the root of the same data, i.e.  $|I_{DS}|^{\frac{1}{2}}$  vs.  $V_G$  plotted on a lin/lin scale. Most of the critical transistor values can then be determined using Equations 1.1 and 1.2.

The threshold voltage  $(V_T)$  is the minimum gate voltage needed to create a conduction path between source- and drain electrodes. Traps at the semiconductor/insulator interface are usually the source of  $V_T \neq 0$  V that is often observed. These traps need to be filled before the conduction channel can be opened, i.e. resulting in a  $V_T \neq 0$  V. The transfer curve is also used to extract  $V_T$ . In the linear region, when  $I_{DS}$  is plotted as a function of  $V_G$ ,  $V_T$  can be found by extrapolating the curve slope, B, and determining its intersection with the  $V_G$ -axis. The same can be done for a transfer curve measured in the saturated region. However, since  $I_{DS}^{sat}$  has a square dependence on the gate voltage (see Equation 1.2), the square root of  $I_{DS}^{sat}$  should be plotted versus  $V_G$ . The same method can then be applied as in the linear regime to determine  $V_T$ . The threshold voltage has been determined using this method and is marked in the transfer curve (saturated regime) plotted in Figure 1.2 (a). The turn-on voltage,  $V_0$ , is defined as the  $V_G$  at which  $I_{DS}$  starts to increase exponentially. The physical origin of  $V_0$  is very similar to  $V_T$  and a change in one is usually followed by a change in the other. The transistor off-current, IOFF, which usually is a result of unintentionally doped semiconductor, is extracted at  $V_0$  (see Figure 1.2 (a)). Another important value that is extracted from the transfer curve is the transconductance,  $g_m$ , or simply put, the transistor gain. It is the ratio between the change in output and the change in input. By using Equations 1.1 and 1.2  $g_m$  is defined as follows, in the linear and saturated regime, respectively:

$$g_m^{lin} = \frac{\partial I_{DS}^{lin}}{\partial V_G} = \frac{W}{L} \mu C_i V_{DS}$$

(1.3)

and

$$g_m^{sat} = \frac{\partial I_{cos}^{sat}}{\partial V_C} = \frac{W}{L} \mu C_i (V_G - V_T)$$

(1.4)

The point on the transfer curve where the slope is the steepest is used to determine  $g_m$ . It then follows that the mobility  $(\mu)$  is easily extracted using Equations 1.3 and 1.4. It can also be directly extracted from the transfer curve, measured in the saturated regime, by using the slope of the extrapolated line, B, (also used to determine  $V_T$ , above) where  $\sqrt{I_{DS}^{sat}}$  was plotted as a function of  $V_G$ . The mobility is then determined as:

$$\mu = \frac{2LB^2}{WC_i} \tag{1.5}$$

It should be noted that  $\mu$  is assumed to be constant at all  $V_G$  in these equations. This is, however, not true for OFETs since, according to the extended Gaussian disorder model for transport in disordered semiconductors, the mobility is dependent on temperature, field and charge carrier density. [37–40] Especially in the IMTs presented in this thesis where ions penetrate the semiconductor, the mobility variations can be even more prominent.

The next thing that can be extracted from the transfer curve is the subthreshold swing, S. It describes how sharply the device turns from off-state to on-state and is given in units of [V/dec]. It is extracted at the same point as  $g_m$  and describes how much change in  $V_G$  is required in order to increase  $I_{DS}$  by one magnitude. Another property that can be determined from the transfer curve is e.g. the speed of the device. This can be done by scanning the transfer curve in both directions and drawing both  $I_{DS}$  curves on top of each other. Hysteresis indicates that the device is slow to switch between off-state and on-state, if the measured current is smaller in the forward sweep compared to the backward sweep. [35,41] This is especially typical for electrolyte gated- and electrochemical transistors, where the relaxation of ion-motion, during operation, can be slow. Hysteresis in the other direction can e.g. indicate some form of reversible or irreversible degradation of the device. [42] Other values that can be extracted from transfer curves are gate-leakage, on-currents, on/off-ratios, etc.

The methods of characterizing transistors presented above are used to characterize the IMTs presented in this thesis, even though the operating mechanism of the IMTs is clearly different than that of the classical MOSFET devices the equations were constructed for. It is, however, a good approximation and it is also common practice in the field of IMTs to do so.

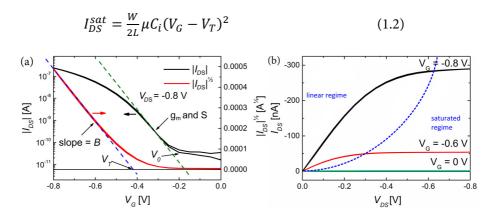

#### 1.2.2. Ion-Modulated Transistors

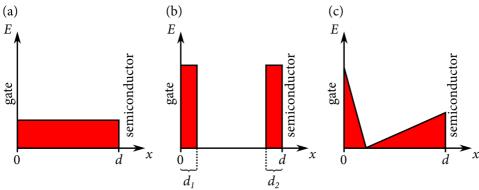

In field-effect transistors, when the gate is being biased, the dielectric layer becomes polarized (the electron distribution, in the bonds between the atoms, rearranges) and the channel in the semiconductor is formed via the field-effect. The gate-dielectric-channel system, plotted in Figure 1.3 (a), can be viewed, in an equivalent circuit, as a parallel plate capacitor where the gate and channel represent the plates and the dielectric the insulator of the capacitor. When the plates are charged the dielectric is polarized (Figure 1.3 (a)) and the capacitance, C, can be calculated using Equation 1.6.

$$C = \frac{k\varepsilon_0 A}{d} \tag{1.6}$$

Here, k is the relative permittivity of the dielectric,  $\varepsilon_0$  is the permittivity in vacuum, A is the area of the plates and d the distance between the plates.

The situation is critically different in an IMT, where the dielectric layer is replaced with an ion-conductor (Figure 1.3 (b)). [43] All transistor types that have the channel modulated by ions fall under the description of IMTs. [14,35,44–46] Terms such as electrolyte-gated transistors (EGTs), electric double layer transistors (EDLTs) and ion-sensitive field-effect transistors (ISFETs) have also been used to define such devices. In this thesis, when talking about transistors, the term *ion-conductor* (ICon) will be used to define the material in the physical space between the gate and the semiconductor in all the IMTs, in the same way as e.g. the term dielectric is used in a classical TFT. In the ICon in the IMTs, the ions are mobile and the equivalent parallel plate capacitor operation changes drastically. During IMT operation two half-reactions occur at the ICon interfaces according to the following description:

When the gate is negatively biased compared to the source and drain electrodes, the first half-reaction entails positive ions (cations) in the ICon attracting to the gate surface creating an electric double layer (EDL), according to the Helmholtz model. [47–50] According to this simple model of the EDL, the gate electrode represents one capacitor plate while the cations attracted to the gate surface represent the other capacitor plate. In reality, the situation is more complicated as the arrangement of the ions at the surface in the ICon is more complicated than a single layer of ions neatly stacked at the surface. The Gouy-Chapman-Stern model [51] e.g. describes a thin inner layer of static ions and a thicker diffusive layer of ions that extend deep into the ICon. However, for the purpose of this discussion, the simple Helmholtz model for the EDL will suffice.

half-reaction second occurs opposite ICon/semiconductor interface whereto the negative ions (anions) are repelled. In order to neutralize the electric field created by these anions, holes are injected into the semiconductor from the source and drain electrodes and a layer of holes is formed at the ICon/semiconductor interface. This layer of holes is also known as the transistor channel. The EDL at this interface then consists of the layer of anions and the layer of accumulated holes. The bulk of the ICon remains charge-neutral and the entire electric field created is dropped across the two EDLs formed at the individual interfaces. This situation, depicted in Figure 1.4 (b) can then be viewed as two parallel plate capacitors connected in series, with the gate and the cations as the plates of one capacitor, separated by a distance  $d_1$ , and the anions and holes as the plates of the other capacitor, separated by a distance  $d_2$ . The resistance of the ICon between the two capacitors is disregarded in this simplified explanation, since in steady state it does not contribute to the capacitance of the system. [52] The individual capacitances  $C_1$  and  $C_2$  can thus be calculated using Equation 1.6,  $d_1$  and  $d_2$ . The total capacitance,  $C_{TOT}$ , (Equation 1.8) can thus be calculated using Equations 1.6 and 1.7.

Figure 1.3. A negative bias is applied on the gates of transistors with different dielectric/ICon layers. (a) The **dielectric** of an OFET is polarized and charges accumulate in the channel, (b) the mobile ions in an **electrolyte** form EDLs at the two interfaces, one of which includes the transistor channel, (c) the mobile ions in the **ionic liquid** (IL) form EDLs at the two interfaces, one of which includes the transistor channel and (d) the mobile cations move to the gate interface creating an EDL, leaving the bulk of the **poly-electrolyte** negatively charged with immobile anions and the transistor channel is formed. The bulk of the ICon in (b) and (c) remains charge-neutral.

$$\frac{1}{c_{TOT}} = \frac{1}{c_1} + \frac{1}{c_2} \tag{1.7}$$

$$C_{TOT} = \frac{C_1 C_2}{C_1 + C_2} = \frac{k \varepsilon_0 A}{d_1 + d_2} \tag{1.8}$$

Comparing Equations 1.6 and 1.8 one can see that the only difference is that d is replaced with  $d_1 + d_2$ . The crucial difference is that d is the separation between the gate and the semiconductor while  $d_1$  and  $d_2$  are the separation between the ions

and holes (or electrons) in the EDLs. Fabricating field-effect driven transistors with small d:s on rough substrates can be difficult without creating pinholes, [53] whereas these potential driven transistors with EDL thicknesses ( $d_1$  and  $d_2$ ) less than one nanometer, [14] independent of the ICon layer thickness, are well suited for fabrication on rough substrates such as paper. Higher capacitances can thus be reached without creating ultra-thin ICon layers or by increasing the relative permittivity of the ICon.

Figure 1.4. The electric field distribution, E, inside the dielectric/ICon layer of a) a traditional dielectric OFET, b) an IMT with electrolyte- or IL-like ICon, having mobile anions and cations, and c) an IMT with poly-electrolytic ICon, having only one mobile ion-species, when the gate is biased. The x-axis represents the gate-semiconductor direction, where 0 indicates the gate/dielectric (gate/ICon layer) interface and d the dielectric (ICon)/semiconductor interface and  $d_1$  and  $d_2$  the EDL thicknesses created at the individual interfaces, respectively.

Typical ICons used are electrolytes where free ion-species are mixed in a solution, usually water. Another, water-free, alternative that can be used as the ICon layer is ionic liquids (ILs). [54-56] In an IL there is no solution in which the ion-species reside. Instead, the ion-species form a sea of dissociated negatively- and positivelycharged ions or associated charge-neutral ion-pairs. In short, ILs can be described as molten salts that melt at moderate temperatures. The capacitive properties of ILs, plotted in Figure 1.3 (c), are generally similar to that of electrolytes [57] and the electric field drops over the EDLs in a similar fashion as the one depicted in Figure 1.4 (b). A third option is a sort of mixture between a classical OFET dielectric and an IL, i.e. a poly-electrolyte, [45,58,59] plotted in Figure 1.3 (d). Here, one of the ion-species is attached to the backbone of a larger polymer network and is essentially immobile, while the counter-ion remains mobile. This results in a situation depicted in Figure 1.4 (c), where the electric field drop is distributed unevenly throughout the bulk of the ICon. This will result in a total capacitance somewhere in the middle of that of a classical OFET and that of an IL-type IMT. This setup can have several advantages, e.g. the polymer backbone can provide a

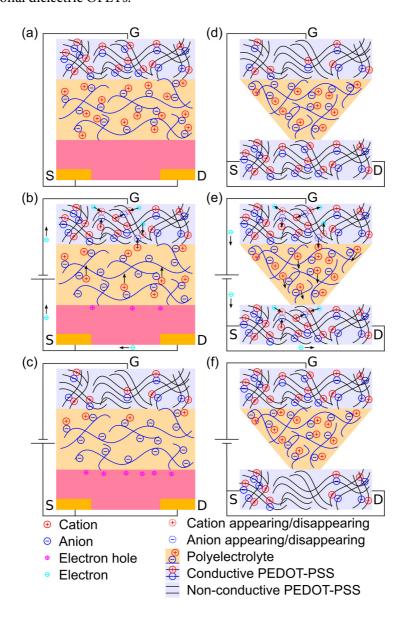

solid matrix for the counter-ion to move around in or the immobile ion can be prevented from penetrating the semiconductor and causing unwanted electrochemistry. This type of poly-electrolyte is used as ICon in the enhancement mode p-channel IMT (EM PIMT) presented in **Paper I**. The same poly-electrolyte is also used as a proton bridge (the term *ion-conductor* is again used to describe the material in the physical space between the gate and the channel) in the depletion mode p-channel IMT (DM PIMT) presented in the same paper. This transistor type has a redox-active PEDOT:PSS as the active layer and the two transistor types operate in very different ways.

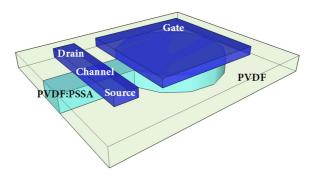

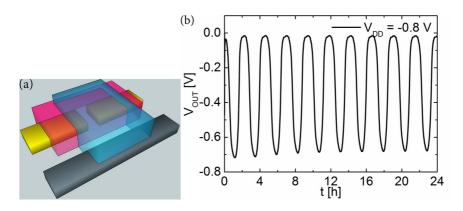

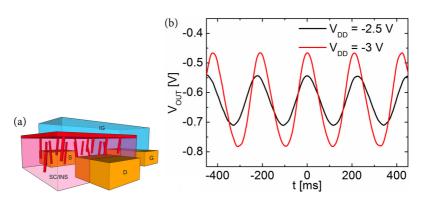

The EM PIMT and the DM PIMT are both built around a self-supporting and insulating (poly(vinylidene fluoride) (PVDF)) membrane that has been functionalized to be ion-conductive poly(vinylidene fluoride) poly(styrene) sulfonic acid (PVDF:PSSA) in selective places. As a result, the membrane can serve as both substrate and ICon in the different transistor types, simultaneously. The EM PIMT is vertically stacked according to the structure illustrated in Figure 1.5 (a) – (c), while the DM PIMT is both vertically and laterally stacked according to Figure 1.6, but for clarity a two dimensional representation has been drawn in Figure 1.5 (d) – (f).

As the ICon of the membrane is here a poly-electrolyte, only one ion (the cation  $H^+$  in this case) is mobile, while the anion is bonded to the polymer backbone and therefore immobile. In the EM PIMT the channel is non-conductive when the gate is un-biased (Figure 1.5 (a)). When the gate is negatively biased, the protons in the ICon migrate towards the gate, penetrate the electro-active PEDOT:PSS gate and electrochemically reduce it. The remaining immobile anions in the ICon create a negatively charged field that is compensated for by positively charged holes accumulating in the transistor channel (Figure 1.5(b)). The channel is highly conducting and no more charge is accumulating (Figure 1.5 (c)).

The DM PIMT, on the other hand, has a conductive channel when the gate is un-biased. The channel is here a stripe of PEDOT:PSS. It is connected ionically to the (also) PEDOT:PSS gate via the ICon (Figure 1.5 (d)). Applying a positive gate bias oxidizes the gate PEDOT:PSS, protons migrate through the ICon, penetrate and electrochemically reduce the PEDOT:PSS channel (Figure 1.5 (e)). This process of reducing the channel turns the transistor off. When there is no more ion-motion in the device, the device is fully turned off (Figure 1.5 (f)).

For all their advantages with high capacitances and low sensitivity to substrate roughness the IMTs are slow to switch between operational states compared to that of traditional dielectric OFETs. [60,61] This is due to the nature of the mobility of the charged ions in the ICon. When an external electric field is applied over the ICon, i.e. a gate bias is applied, ions migrate inside the ICon as a

response to the electric field and the EDLs are eventually formed at the individual interfaces. This process is the rate limiting factor that makes them slower than traditional dielectric OFETs.

Figure 1.5. A schematic cross-section of an EM PIMT is depicted in (a), (b) and (c) and a DM PIMT in (d), (e) and (f). Light blue, yellow and pink areas indicate PEDOT:PSS, polyelectrolyte and P3HT, respectively and gold S- and D electrodes. The figures on top represent the devices in their natural un-biased states, the middle figures when the devices are being turned on and off, respectively and the bottom figures the devices in the on- and off-states, respectively.

Figure 1.6. Device setup of the enhancement mode IMT. The white and light blue represents the patterned membrane containing both the insulating PVFD (white) and the ion-conducting PVDF:PSSA (light blue). The dark blue represents the drop casted PEDOT:PSS that make up the gate-, source- and drain electrodes and also the transistor channel.

A second and even more complicated process that can occur in IMTs with mobile ions is that the ions not only move to the ICon/semiconductor interface and create an EDL, but they can also penetrate the semiconductor and electrochemically dope it. [14] Further, the ions continue to move deeper into the semiconductor doping the entire bulk. This process of ion-migration inside the semiconductor is even slower than the ion-migration in the ICon discussed in the previous section. As the doped parts of the semiconductor are conducting and contribute to the source-drain current, high throughput currents are now achievable. This device can now be said to be electrochemical since the source-drain current flows through the bulk of the semiconductor, and not only at the ICon/semiconductor interface.

The time domains of the ion-migration in the ICon, the EDL formation and the last ion-migration in the semiconductor are strictly different and vary depending on the materials used; especially important are the internal resistance of the ICon and the ion-mobility in the semiconductor. This is one of the most important reasons why electrochemistry is unwanted in IMTs, and also why poly-electrolytes are used as the ICon layer in some transistors.

## 1.3. Logic Circuits

The next step that naturally follows after the basic electronic building blocks, such as transistors, have been created is building logic circuits. [62] In this chapter the focus will be on presenting simple inverters and continuing onto more complicated circuits, such as ring-oscillators, NOR-gates and finishing with memory devices, such as SR-latches.

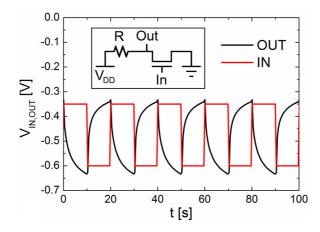

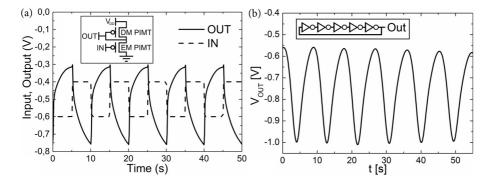

#### 1.3.1. Inverters

The inverter is a logic NOT-gate [63] that returns a state that is opposite to the input state, i.e. if the input is *true* the output will be *false* and vice versa. An inverter can be built using one, two, three or even more transistors, but the simplest model incorporates just one transistor. This can be done with any type of transistor (n-channel, p-channel, etc.) combined with a resistor, as long as the transistor has good enough electrical characteristics so that the inverter output is larger than the input. This is a requirement since more than one inverter is needed in order to create logic, i.e. one inverter must be able to supply the next one with current without signal decay. The output signal must also have an off-state lower than the off-state of the input and an on-state higher than the input on-state (see Figure 1.7.) The signal would otherwise drift in one direction after each inverter-stage making the electronic device useless. The basic inverter has four terminals: ground, supply voltage, input and output. The first two are typically constant while the latter two usually vary with time. A single-transistor (p-channel) inverter can be seen as inset in Figure 1.7.

Figure 1.7. An example of the input- (red curve) and output voltages (black curve) of an inverter. It is important that the lowest output voltage is lower than the lowest input voltage and the highest output voltage is higher than the highest input voltage. The inset shows the connection diagram of the inverter.

Depending on the voltage applied to the transistor gate (inverter input) the transistor channel resistance ( $R_{SD}$ ) will either be high ( $R_{SD,ON}$ ) or low ( $R_{SD,OFF}$ ).  $R_{SD}$  refers to the resistance between source and drain. The inverter resistor (R) must be chosen so that its value lies between  $R_{SD,ON}$  and  $R_{SD,OFF}$  in order for the inverter to work. A high (absolute) voltage applied to the input will make the channel highly conductive and all current will flow between ground and the inverter output, since

$R > R_{SD,ON}$ . When a low (absolute) voltage is applied to the input, the transistor channel will be highly resistive,  $R < R_{SD,OFF}$ , and all current will flow between the supply voltage,  $V_{DD}$ , and the inverter output. It is now very important to have good transistor characteristics. For example, a poor on/off-ratio will make the different resistance values (R,  $R_{SD,ON}$  and  $R_{SD,OFF}$ ) too close to each other and result in some current flowing through the transistor, when all current should be flowing through the resistor and vice versa.

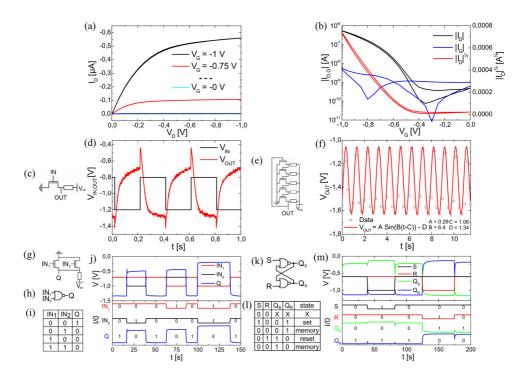

To alleviate some of these effects another transistor can be incorporated into the inverter replacing the static resistor. The new transistor must now be an n-channel device in order for the replacement to be useful. This type of setup is called a complementary-symmetry metal-oxide-semiconductor (CMOS) technology. [62–66] The advantage here is that the current will always be flowing through either of the transistors, never through both at the same time (only during switching). For the single-transistor inverter some current was always flowing from the supply voltage directly to the ground, creating excess heat. The CMOS inverter also switches faster than the single-transistor inverter. These are some of the reasons why CMOS technology has become so widely used, especially in integrated circuitry. The performance of the transistors used will dictate how well the inverters will operate. The most critical properties are the power consumption and switching speed. These depend directly and most importantly on the transistor gate-leakage, on/off-ratio and sub-threshold swing. The different inverter types used will be presented in **Papers I**, **II** and **III**.

#### 1.3.2. Ring-Oscillators

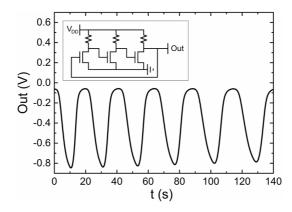

The ring-oscillator is a row of inverters connected in series and the output of this series is fed back to the input of the ring-oscillator creating an endless loop of inverters (see inset of Figure 1.8.). [62–65] In order to achieve an oscillation an uneven number of inverters must be present in the loop, otherwise the device would constantly be in a stable state. In a loop of an odd number of inverters every inverter will constantly be switching the input of the next one. The switching speed will be a function of the gate-delay of each individual inverter-transistor. The gate-delay is defined as the time it takes to switch one transistor from off-state to on-state and vice versa. The frequency of the oscillation of the output of the ring-oscillator gives the propagation delay time of the oscillator according to Equation 1.9:

$$P = 2Nt_n \tag{1.9}$$

where P is the oscillation period, N is the number of inverters in the oscillator and  $t_p$  is the propagation delay time per inverter-stage. The last one  $(t_p)$  can be described as the phase-shift between the input and output of one individual inverter. A typical output of a ring-oscillator can be seen in Figure 1.8. The ring-oscillator setup is a useful demonstrator when developing new transistor types. There are several factors that need to be fulfilled for the ring-oscillator to function properly. Firstly, the individual inverters must amplify and invert the input signal. They must have the input levels within the output levels according to the description in Section 1.3.1. Many functioning transistors must be fabricated at the same time and they must have similar properties for the oscillator to operate. A working ring-oscillator is a strong indicator of whether the new transistor model can be a useful electronic component or not. The oscillation frequency also gives important information about the switching speed of the transistor. Several different ring-oscillators are presented in this thesis in **Papers I**, **II** and **III**.

Figure 1.8. Typical output curve of a three-stage ring-oscillator with the connection diagram as inset.

#### **1.3.3. NOR-Gates**

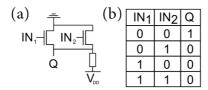

The NOR-gate [62–66] is another example of basic logic gates that are required when building any type of electronics. To build one using OFETs at least two transistors are needed, when using n- or p-channel metal oxide semiconductor (NMOS or PMOS) technology only. The same advantages holds true for the NOR-gate as for the inverter when utilizing CMOS; faster switching and less power consuming devices can be built. When using CMOS usually four transistors are needed to create the NOR-gate. In this thesis, however, PMOS-only NOR-gates are created and in such a device two p-channel transistors and one resistor is required for the gate to function correctly. The device setup can be seen in Figure 1.9 (a).

Figure 1.9. (a) The connection diagram of a NOR-gate constructed using two p-channel transistors and one resistor and the corresponding (b) truth table.

The two transistors are connected in parallel and the resistor, R, in series. The supply voltage,  $V_{DD}$ , is connected to R, the transistor drains are connected to the ground, the inputs  $IN_I$  and  $IN_2$  are connected to the transistor gates and the output Q is connected to the transistor sources. When the resistance of the transistor channels in off-state ( $R_{SD,OFF}$ ) is higher than R and smaller in on-state ( $R_{SD,ON}$ ), ( $R_{SD,OFF} > R > R_{SD,ON}$ ), the current will flow between  $V_{DD}$  and Q only when both transistors are in off-state and between ground and Q in all other cases. The truth table for the NOR-gate is shown in Figure 1.9 (b). This NOR-gate set up may cause the two-transistor component to have three distinct resistance levels;  $R_I$  when both transistors are turned on,  $R_2$  when one or the other transistor is turned on and  $R_3$  when both transistors are turned off ( $R_1 < R_2 < R_3$ ). The closer  $R_I$  is to  $R_2$ , the better. Otherwise the Q off-state will be split in two distinct voltage levels reducing the NOR-gate's usefulness. Also, if  $R_3$  is too close to  $R_I$  and  $R_2$  the distinction between Q on- and off-state will be difficult.

These types of difficulties can arise if the characteristics of the transistor (on/off-ratio, sub-threshold swing, gate-leakage) are poor or marginal, which is typical when working with paper-based transistors. An environmentally friendly NOR-gate constructed on paper is presented in **Paper III**.

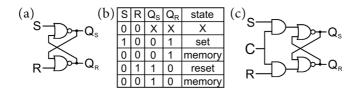

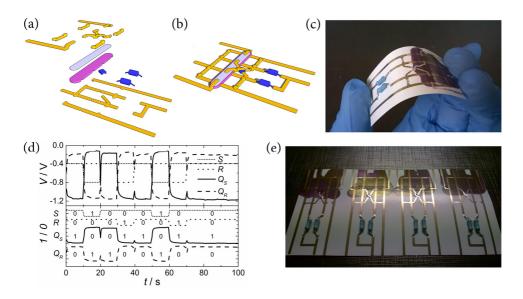

#### 1.3.4. SR-Latches

The SR-latch [63,64,66] is one of the simplest forms of memory element that can be implemented using PMOS technology only. The function of the latch is to be able to retain one bit of memory. This operation requires, in this case, two sets of NOR-gates that have their outputs connected in a feedback loop according to Figure 1.10 (a). In this type of setup the outputs will depend not only on the current inputs but also on previous inputs, hence the memory effect. The truth table for this device can be seen in Figure 1.10 (b).

Figure 1.10. (a) The connection diagram of an SR-latch. Two NOR-gates are connected to create the latch. (b) The truth table corresponding to the latch depicted in (a). (c) The connection diagram of a clocked SR-latch with two additional AND-gates.

The basic operation of the SR-latch is that two separate states (*set*, *S*, and *reset*, *R*) can be applied to the latch. The two states can be set by applying 1 and 0 or 0 and 1 to the *S* and *R* inputs. The memory effect comes from the fact that the state stored in the latch is retained even when 0 and 0 are applied on the inputs. The outputs of the SR-latch,  $Q_S$  and  $Q_R$ , are always each other's complements due to the latch setup, hence,  $Q_S = Q_R$  is impossible, and even further, S = R = 1 is a forbidden state. The SR-latch is a transparent latch. This means that the output is immediately affected by a change at the inputs. This can be an unwanted feature, e.g. in shift registers, since several consecutive latches would see their states immediately propagated through the entire series, voiding the memory effect. This effect can be avoided by adding a separate clocking device to each SR-latch, e.g. by adding two AND-gates to the inputs of the latch, according to Figure 1.10 (c). This clocking, C, terminal allows for whatever state that is set to the S and R inputs not to propagate to the  $Q_S$  and  $Q_R$  outputs until C is set to 1. This feature makes the SRlatch, in this form sometimes called a clocked flip-flop, opaque and allows for the creation of e.g. shift registers. A shift register is a memory device that can be used to write, store and read a series of data bits on.

The SR-latch is a logic circuit that is fairly complicated to build, i.e. it contains many transistors, resistors and inter-connections. Being able to build such a complicated device using our transistors, is a feat that demonstrates that our transistors will also work in other, more complicated circuits. The same type of difficulties, stemming from poor gate-leakage, sub-threshold swing, on/off-ratio, are also associated with creating SR-latches as was described for the NOR-gate in the previous chapter. They are, however, magnified here since twice the number of transistors (each device introducing its own problems) are used here compared to the previous devices.

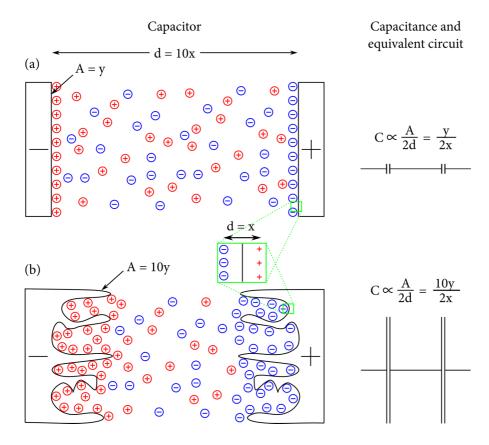

## 1.4. Supercapacitors

The supercapacitor (SuC) is an energy storage device constructed as a parallel plate capacitor. There are two major SuC types, namely electrostatic and electrochemical SuCs. [67,68] An additional third subgroup is the combination of the two above mentioned types. The names refer to the nature of the energy storing mechanism. In the SuCs presented in this thesis no electrochemistry occurs and these SuCs are therefore of the electrostatic kind. A SuC has the same principal physical shape and electrical characteristics as an ordinary parallel plate capacitor. The capacitance is, however, much larger than an ordinary capacitor. In the SuC the dielectric is replaced with an ion-conductor (ICon) in the same manner as was done for the IMT presented in Section 1.2.2. As a result of the EDLs a high capacitance is achievable in a SuC with sub-nanometer ds according to Equation 1.8. The situation has been drawn in Figure 1.11 (a) including the equivalent circuit and capacitance, again leaving out the ICon resistance, as was done in Section 1.2.2. In order to increase the capacitance, a situation depicted in Figure 1.11 (b) has be utilized. Here, the electrodes have been replaced with a porous, high surface area material (on the order of 1000 m<sup>2</sup>/g). This will lead to further increase as Equation 1.8 still holds true and the surface area is increased.

The word 'super' in supercapacitor is partially used since the electrodes in such devices have an extremely high 3D surface area, e.g. AC or nanotubes, and partially due to the high capacitances that are associated with the electrostatic and/or electrochemical storage of charges on the individual capacitor plates. There are limits on how large surface areas can be created. Firstly, the size of the ions determines how small the pores can be made. One must take into account that in SuCs in general there can always be present a complex ordering of cations and anions in layered-, micelle- and/or other complex structures. [47–50,69,70] Secondly, the conductivity of the electrodes must remain high enough to carry charges from the outermost edges of the AC to the charge collectors. Otherwise, all unconnected electrode area will only create excess insulating layers that diminish the capacitance. Thirdly, the pathways to the electrodes must be large enough to facilitate the complex ion clusters to reach the electrode surface deeper in the electrode. Bottlenecks here will result in large internal resistances of the capacitor resulting in slow-chargeable devices.

The situation becomes more complicated when the electrode material is easily reducible or oxidizable. Then the ion can, even in aqueous ICon, reach the electrode surface and electrochemically oxidize it with electron charge-transfer. This Faradaic method of storing charge on the electrode is more efficient than the non-Faradaic EDL. This method of storing energy is sometimes referred

to as a pseudocapacitance. [68,71] Even though these energy storing methods (especially the Faradic kind) are similar to that of re-chargeable batteries they are both faster and can be charged and re-charged many more times (>100 000) when compared to the batteries. [71] The reason is that only electrostatic charge transfer between electrode and ICon can occur, while in the batteries both chemical and structural changes of electrochemical reactive materials occur when the electrochemically stored energy is being released. Repeated cycling eventually degrades the electrode materials, reducing the battery cycling capability to a few

Figure 1.11. The difference in capacitance of two different biased capacitor setups if x and y remain constant. (a) The situation when the dielectric is replaced with an ICon, with mobile positive (red) and negative (blue) ions, has been drawn. EDLs are formed at the interfaces and the inset illustrates that d is now the EDL thickness, i.e. the separation between the electrode and the ions at the surface. On the right the equivalent circuit has been drawn and the capacitance that is proportional to y/2x. (b) When the electrode area is increased but the situation is otherwise similar to (a) the equivalent circuit, drawn on the right, will be proportional to 10y/2x.

thousand. Due to the fast charging mechanism of the SuCs, large amounts of current can be extracted from them quickly, making them suited for applications where sharp power peaks are required. Compared to conventional batteries, SuCs have about one tenth the energy densities, but at the same time, ten times the power density. SuCs can, however, also discharge their energy slowly making them suitable for a wide range of applications. They can serve as backup power sources for memories, microcomputers and clocks, they can serve as the main power for toys, emergency door opening and pulse power for starting of motors. They can also serve as alternating power sources where the energy is stored and used repeatedly, e.g. in solar cells during day/lamps during night or in any form of transportation where power is used during acceleration and recaptured during deceleration. The list is endless. One should, however, keep in mind that SuCs are best utilized when they are used in conjunction with other, conventional, power sources. The SuCs can e.g. handle sharp power peaks, when needed, and a leave the base power needs to the conventional battery. [68,71]

## 2. Experimental

The materials used to create the devices in this thesis are presented in this chapter. In Section 2.1.1 the different substrates and their preparation is described and in Section 2.1.2 the electrodes used in the transistors and supercapacitors are described. In the following Sections 2.1.3 and 2.1.4 the preparation of the semiconductors and ICons used are presented in detail. The different electrical and optical characterization methods utilized are presented in Section 2.2.

## 2.1. Materials and Methods

#### 2.1.1. Substrates

The choice of substrate in this thesis has been a strong restricting factor when it comes to the possible choices of device structure, materials and fabrication techniques used, especially when it comes to the transistor. The transistor is especially sensitive to the roughness of the substrate since an uneven semiconductor layer causes trapping in the transistor channel, resulting in threshold voltage shifts, slow switching devices and increased bias stress effects. As the alternatives of environmentally friendly substrates that are also compatible with roll-to-roll (R2R) printing techniques are few, completely novel substrates have been developed at Åbo Akademi University.

#### 2.1.1.1. PVDF

The substrate generally called the "membrane" in this thesis is the flexible, mechanically durable and chemically resistant poly(vinylidene fluoride) (PVDF). [72–74] This partially fluorinated insulator acts as the substrate for the transistors presented in **Paper I**. Several different thicknesses of the base membrane (containing different pore sizes) are available, but the membranes used in this thesis have a thickness of 200 µm and a pore size of 200 nm. The chemical structure of this material can be seen in Figure 2.1 (a). What makes this substrate novel is that it can be further functionalized to be ion-conductive and therefore also serve as ICon in the transistors. As this functionalization process can be made in selective parts, only part of the base membrane will be ion-conductive. This patterned membrane can now serve as both substrate and ICon in the DM PIMTs and EM PIMTs models presented in **Paper I**. The process is described in more detail in section 2.1.4.

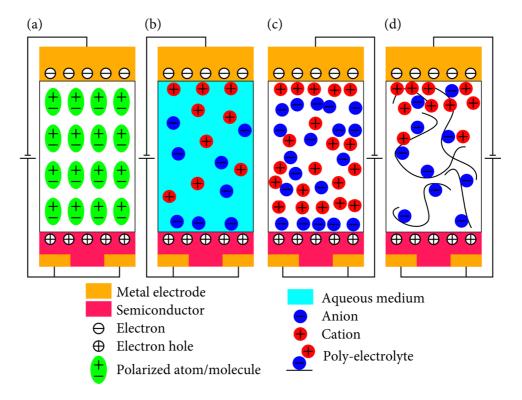

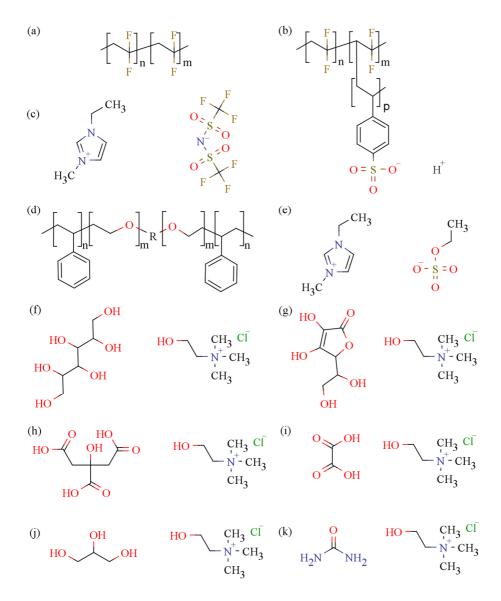

Figure 2.1. The chemical structures of the different ICons used in this thesis and some of the materials used to create them; (a) PVDF, (b) PVDF:PSSA, (c) EMIM:TFSI, (d) PS:PEO:PS, (e) EcoEng, (f) CSorb (Sorbitol + ChoCl), (g) CAsco (Ascorbic acid + ChoCl), (h) CCitr (Citric acid + ChoCl), (i) Oxaline (Oxalic acid + ChoCl), (j) Glyceline (Glycerol + ChoCl) and (k) Reline (Urea + ChoCl).

#### 2.1.1.2. Paper

The second novel substrate used in **Papers II** and **III** is the multi-layer pigment coated paper developed and fabricated at Åbo Akademi University. [75] It has both smoothening- and barrier layers fabricated using a pilot-scale slide curtain coating technique. A pre-coated finepaper (StoraEnso Lumipress 115) was used as the base

paper and the final coated paper was calendered to achieve further smoothness. The paper contains Kaolin, mineral pigment and latex and has a surface RMS smoothness of 50-80 nm on a 10000  $\mu m^2$  area. The smoothness of the paper is close to that of Mylar A.

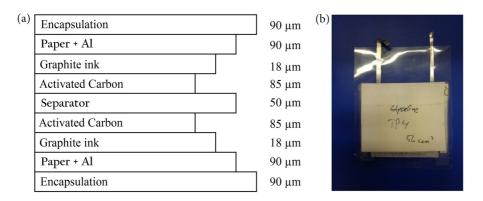

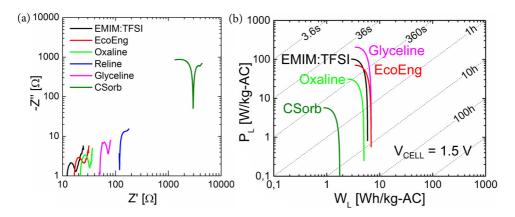

The paper substrate used in the "commercial" SuC structure in **Paper IV** is aluminum coated paper (Walki® Pantenna Laminate). The paper was originally developed for use as substrate for RFID-antennas and the paper has a thin coat of plastic on both sides, one of which has an aluminum coat. The aluminum serves as charge collector for the graphite/activated carbon electrodes in the SuC.

#### 2.1.1.3. PET

Poly(ethylene terephthalate) (PET) has been used in several devices presented in this thesis. PET is a low-cost, flexible, visually clear and commercially available polyester film that is compatible with roll-to-roll fabricating processes. The PET films (Melinex 506, Pütz GmbH + Co. Folien KG) used in this thesis are 100  $\mu m$  thick and have a surface root mean square surface roughness around 5 nm. Before use the films were cleaned with de-ionized water, acetone and iso-propanol in ultra-sonic baths.

#### 2.1.1.4. Glass

Glass as a substrate has been used sparsely in the experiments in this thesis as it is not suitable for R2R-manufacturing processes nor is it otherwise suitable for low-cost, biodegradable applications. In some experiments, however, where material properties are investigated and smooth, transparent and otherwise flawless substrates are needed, glass has been chosen as the substrate of choice. Standard laboratory glass slides, cleaned with de-ionized water, acetone and iso-propanol in ultra-sonic baths, were used in those cases.

#### 2.1.2. Electrodes

#### 2.1.2.1. Gold

The choice of electrode material is especially critical when working with low-voltage electrolytes. The work function of the gate electrode can be changed up to 1 eV by changing the gate material, resulting in large changes in threshold-voltage. [76] As the voltage window of the transistor is comparable to the gate work function change, the transfer characteristics of the transistor will change drastically as a result. It has been shown that the shape of the transfer curve changes when the gate material (and  $V_T$ ) is changed. [41,76–78] In order to maximize the subthreshold voltage swing, gold has been chosen as the gate material in the

transistors where a metal gate was used. Gold is also chemically inert, which is important when working with ICons. The source-, drain- and gate electrode material used in all transistor structures in this thesis, except in the DM PIMT and EM PIMT structures, is gold. The gold electrodes were applied using a few different fabrication methods. The source- and drain electrodes have all been applied by vacuum evaporation through suitable shadow masks. When gold was used as source and drain material in transistors in this thesis, 30 μm long and 1500 μm wide channels were fabricated. Three different methods for applying the gate electrode have been used. The first one was used in vertical transistor structures. Here, the gate electrode was applied by direct evaporation on top of the ion gel. The second one was used in lateral transistor structures. Here, the gate was applied by indirect evaporation, i.e. by evaporating gold on top of a piece of sticky tape that was subsequently attached on top of the semiconductor, on the side of the channel, prior to the ICon application. The third one was used in some experiments where the probing stations gold probe was used directly as the transistor gate electrode and no separate gate electrode was ever manufactured.

When analyzing the different ICons with impedance spectroscopy, gold was used as the electrode material in some of the experiments. Here, the same evaporation method was used as above, except that a different shadow mask was used to produce two circular electrodes of 1 cm in diameter. The electrodes were then used to sandwich the ICon being investigated to create a parallel plate capacitor.

#### 2.1.2.2. PEDOT:PSS

Poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate) in water solution (1.2 wt.%) (Clevios<sup>TM</sup> P) (PEDOT:PSS) is used both as the active layer [72] and as electrode material [79,80] in the transistors presented in this thesis. See a more detailed description of PEDOT:PSS in Section 2.1.3.3.

#### 2.1.2.3. Activated Carbon

In the supercapacitor devices (Section3.4) presented in this paper, two different types of activated carbon (AC) electrodes (the "standardized" and the "commercial" SuC) were used. The standardized electrode used was a 1×1 cm² reference electrode that could be used in measurements where various properties of different ICons were characterized. An important factor here is that the electrodes should be as similar as possible when, for instance, comparing the capacitance of a set of different ICons. When the electrodes for the commercial SuC were fabricated, similar pore sizes, graphite densities, electrical properties, etc. as for the standardized SuC were strived for, while having an ink that could be rotary screen printed on a pilot scale printer and result in AC electrodes that would

not delaminate during or after fabrication. The main goal here was to increase the amount of charge that can be charged to, stored on and extracted from the SuC, and to that end the electrode area was increased to 112 cm<sup>2</sup>.

The basic aim is then, when fabricating both electrode types, to achieve as high a specific surface area (SSA) for the AC as possible. [71,81] For a typical AC, the SSA ranges between 1000 and 3000 m<sup>2</sup>/g. [81,82] The conductivity of the electrodes is also a crucial property that needs to be optimized in order to achieve the best possible EDLs at the electrode/ICon interfaces. Therefore, a binder for the AC, suitable for this purpose, must also be chosen. Chitosan was chosen since it is biodegradable and non-toxic. [83] Although chitosan is not itself conductive, it has been shown that by mixing in enough AC the resulting blend will be electrically conductive. [84] Also, it has been shown that introducing chitosan into an AC matrix increases its carbon capture capability. [85] Another important factor to consider is the pore sizes in the electrodes. If the pores are too small, ions (or ion clusters) will have difficulty entering them, resulting in weak EDLs. If the pores are too large, the effective surface area will be small, which will have the same result. This is also a reason why different ICons, with different size and/or charge, but similar capacitances, perform differently when using AC electrodes.

Two different substrates were used for the two SuC structures; PET and paper. For the standardized SuC, PET was used in order to achieve consistent electrode properties and for the commercial SuC, paper was used in order to achieve low-cost and environmentally friendly devices. The PET substrate was laminated with a 7 µm thick aluminum layer, whereas the paper substrate had a thin plastic coat on both sides, one of which was laminated with a layer of aluminum. In both SuC structures, a layer of dense graphite (Acheson PF407A) was printed on top of the aluminum layer, in order to shield the charge collector/emitter from corrosion, as the polar ICons, used in the devices, contain water and chlorides. On top of the graphite a layer of AC (Norit DLC Super 30) is printed to serve as the active, large area, electrode. The water-based AC ink contained chitosan binder (ChitoClear fg90, Primex) in a weight ratio of 1:20.

The graphite and AC were printed using screen printers in both SuC models. The standardized version was printed on a laboratory scale, whereas the commercial one was printed using a rotary screen printer in a pilot scale printer. The same printing inks were used in both SuC structures. In the standardized version, after the graphite was printed, it was dried at 95 °C. After that a layer of AC was printed on top of the graphite layer and dried in room temperature. In the commercial SuC, the graphite was printed at 2 m/min using a screen mesh 64

threads/inch followed by 2 minutes of drying in 140 °C ovens. The AC was printed on top of that layer using the same mesh, speed and heating. The roll of electrodes was then transferred to a new machine where two extra drying steps were performed. These steps were performed at 1.5 m/min using a 5 kW IR lamp (12 seconds) and 140 °C ovens (2 minutes). These electrodes were then used, in combination with ICons (Section 2.1.3.4), to create the environmentally friendly supercapacitors presented in Section 3.4.

#### 2.1.3. Semiconductors

#### 2.1.3.1. P3HT

Polymeric organic semiconductors were chosen as the semiconducting material in all enhancement mode transistors presented in this thesis, as they are solution-processable at room temperature and thus compatible with R2R-compatible fabrication techniques and, most importantly, have good semiconducting properties. Solid films of organic semiconductors also have the advantage of being highly flexible, which is required for the membrane- and paper substrates used in this thesis. [86]

The charge transport occurs both along the pi-conjugated backbone of the individual polymer molecule, and hopping from molecule to molecule. [38,87] In order to make the polymer conducting, charges need to be injected into it or induced by means of chemical- or electrochemical doping. [88] All three methods can conceivably be present in one and the same transistor: by applying a gate bias, charges are injected into the SC in the channel from the source electrode; if the substrate contains OH-groups, they can penetrate and chemically dope the semiconductor; in an IMT, ions from the ICon can penetrate and dope the semiconductor during operation via electrochemistry.

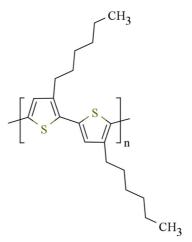

The most prominent semiconductor used in the enhancement type transistors in this thesis is rr-poly(3-hexyltiophene) OS1100, acquired from Sigma-Aldrich/Plexcore, P3HT. The chemical structure of P3HT has been plotted in Figure 2.2. This semiconductor has been used in **Papers II** and **III**. It was dissolved in DCB and spray casted onto the paper substrate. It was also used to create the semiconductor/insulator blends used in the papers. The semiconductor (and insulator) was dissolved in CB before the blend was spin- or drop casted onto the paper substrate. Other, more environmentally friendly solvents that have been used to dissolve P3HT in, are p-xylene and toluene. The spray casted films were estimated to be around 300 nm thick.

Figure 2.2. Chemical structure of P3HT.

#### 2.1.3.2. PQT-12

Another semiconductor that has been used is poly(3,3"-didodecyl quarter thiophene) acquired from American Dye Source Inc., PQT-12 (Figure 2.3). It has longer side chains than P3HT and is shown to have better air stability properties as well as higher carrier mobility than P3HT. [89] The electronic properties are otherwise similar to those of P3HT. [90] PQT-12 was used to create the enhancement mode transistors presented in **Paper I**. The semiconductor was dissolved in DCB and spray casted onto the membrane substrate creating roughly 200 nm thick semiconductor films.

*Figure 2.3. Chemical structure of PQT-12.*

#### 2.1.3.3. PEDOT:PSS

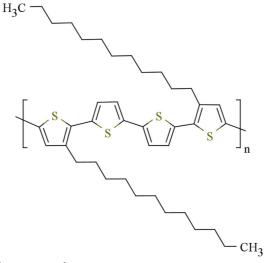

The organic redox-active (PEDOT:PSS) is conducting in its normal state [91] and must be (electro)chemically reduced in order to make it non-conductive. Due to this fact PEDOT:PSS has been used both as electrode material and the active material in the transistors presented in **Paper I**. The chemical formula of PEDOT:PSS can be seen in Figure 2.4. The positive charge carriers in PEDOT<sup>+</sup> are balanced by the counter anion in PSS<sup>-</sup>. The concentration of polarons, responsible for the charge transport along the PEDOT polymer chains, is then dependent on the balance between neutral and reduced PSS. This situation is described by the red-ox reaction:

$$PEDOT^{+}PSS^{-} + H^{+} + e^{-} \Leftrightarrow PEDOT^{0} + H^{+}PSS^{-}$$

In its natural state (in ambient air) PEDOT:PSS has both oxidized (PEDOT<sup>+</sup>) and reduced (PEDOT<sup>0</sup>) parts. [91] Oxidizing it further will increase the conductivity. Over-oxidation can, however, occur at higher potentials, causing permanent loss of conduction due to permanent disruption of pi-conjugation. [92–94] Reversible reduction, on the other hand, is accomplished by the addition of protons and electrons, i.e. by reducing the amount of polarons available for charge conduction. To increase the conductivity, a small amount of ethylene glycol (typically 5%) has been added to the PEDOT:PSS/water solution. The reason for this has been explained as a better ordering of the conducting PEDOT:PSS chains, and expulsion of the non-conducting PSS groups, during the solvent evaporation process. [80,95,96]

All PEDOT:PSS layers presented in this thesis are applied by drop casting. The layout of the gate and channel (including source and drain electrodes) of the DM PIMT can be seen in Figure 1.6. During operation the protons move between the gate PEDOT:PSS and channel PEDOT:PSS, simultaneously reducing one and oxidizing the other, depending on the external electron flow supplied by an external power source. The DM PIMT has the gate electrode ionically connected to the channel, via the patterned membrane's poly-electrolyte, so that the gate PEDOT:PSS acts as a conductor and the channel PEDOT:PSS as active material. The gate area is about ten times larger [97] than the channel area (defined as the PEDOT:PSS in contact with the ICon). This is done so that the channel can effectively be reduced without over-oxidizing the gate PEDOT:PSS. Also, the thinner the channel PEDOT:PSS layer is, the easier it is to reduce it and re-oxidize it during operation.

Figure 2.4. Chemical structure of PEDOT:PSS.

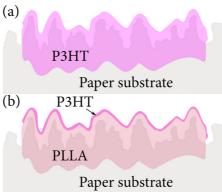

#### 2.1.3.4. Blends

In Paper II different concentrations of poly(3-hexylthiophene):poly(L-lactic acid) (P3HT:PLLA) blends were used to create vertically phase-separated semiconductor/insulator (SC/INS) layers [98] in the transistor, in order to speed up the device switching speeds. The basis for this idea was that by replacing the pure semiconductor layer with a SC/INS layer the thickness of the SC would be reduced. The advantage of this is that the electrochemical process that occurs during transistor operation will be faster when the SC layer is thinner. The electrochemical doping of the SC will be faster, if the ions penetrating it have a shorter distance to travel, which is the case when the SC layer is thinner. As a result of this the switching of the transistor will be faster. As we are aiming towards environmentally friendly devices, the polymer insulator PLLA (124000 g/mol, HM1011, T&L Finland Oy) was chosen as it is biodegradable, non-toxic and cheap. [99] The chemical structure of PLLA can be seen in Figure 2.5.

Figure 2.5. Chemical structure of PLLA. Substituting the positions of the hydrogen, going into the page, and carbon, coming out of the page, would create the other chiral form of PLA, namely PDLA.

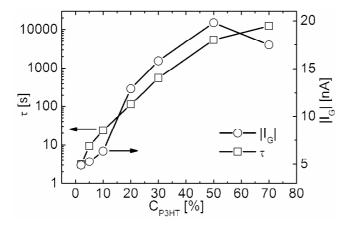

Other physical demands were also required of the insulator; it had to be solvable in the same solvent as P3HT, it had to have suitable surface energies compared to that of P3HT and the paper substrate, and finally, its solubility (in the chosen solvent) had to be lower than that of P3HT. All of the above mentioned requirements were fulfilled by PLLA and the solvent chosen was chlorobenzene (CHROMASOLV\*, for HPLC, 99.9%, Sigma-Aldrich) (CB). PLLA is a mixture of poly(lactid acid) in both L- and D-chiral forms. The mixture used is 95 mol% L-form and 5 mol% D-form. Other concentrations were also tested but resulted in either badly performing devices or materials that would not dissolve in CB. A more detailed analysis of the blend is made in Section 2.1.3.4 and Paper II.